# Device Perspective for Black Phosphorus Field-Effect Transistors: Contact Resistance, Ambipolar Behavior, and Scaling

Yuchen Du, Han Liu, Yexin Deng, and Peide D. Ye\*

School of Electrical and Computer Engineering and Birck Nanotechnology Center, Purdue University, West Lafayette, Indiana 47907, United States

ABSTRACT Although monolayer black phosphorus (BP), or phosphorene, has been successfully exfoliated and its optical properties have been explored, most of the electrical performance of the devices is demonstrated on few-layer phosphorene and ultrathin BP films. In this paper, we study the channel length scaling of ultrathin BP field-effect transistors (FETs) and discuss a scheme for using various contact metals to change the transistor characteristics. Through studying transistor behaviors with various channel lengths, the contact resistance can be extracted

with the transfer length method (TLM). With different contact metals, we find out that the metal/BP interface has different Schottky barrier heights, leading to a significant difference in contact resistance, which is quite different from previous studies of transition metal dichalcogenides (TMDs), such as MoS<sub>2</sub>, where the Fermi level is strongly pinned near the conduction band edge at the metal/MoS<sub>2</sub> interface. The nature of BP transistors is Schottky barrier FETs, where the on and off states are controlled by tuning the Schottky barriers at the two contacts. We also observe the ambipolar characteristics of BP transistors with enhanced n-type drain current and demonstrate that the p-type carriers can be easily shifted to n-type or *vice versa* by controlling the gate bias and drain bias, showing the potential to realize BP CMOS logic circuits.

KEYWORDS: black phosphorus · phosphorene · Schottky barrier transistor · contact resistance · short-channel effect

ow-dimensional materials are garnering more and more interest in condensed-matter physics, materials, and device communities. They provide a new class of materials that are atomic-layer thick. Graphene, boron nitride, and transition metal dichalcogenides (TMDs) provide the ideal metal, insulator, and semiconductors as three basic building blocks for any device applications. 1-15 Transistors built on monolayer or few-layer MoS2, the most studied TMDs, are the optimal forms of ultra-thinbody field-effect transistors (FETs) with an ideal structure to protect against the shortchannel effects.<sup>9,13</sup> Also, the comparatively heavier effective mass of the MoS2 allows transistors to have lower direct sourcedrain leakage current, increased drive current, and enhanced transconductance when benchmarked against the ultra-thin-body Si transistors at their scaling limit.<sup>14</sup> However, the carrier mobility of MoS2 is much lower than that of graphene or traditional semiconductors.<sup>16</sup> Due to the presence of S vacancies and strong Fermi-level pinning near the conduction band,<sup>17</sup> MoS<sub>2</sub> transistors monotonically show n-type FET characteristics even when using high-workfunction contact metals.<sup>18</sup>

The quest for p-type 2D materials is needed to build energy-efficient 2D electronic or optoelectronic devices such as CMOS, tunneling FETs, photodetectors, and solar cells beyond 2D Schottky barrier FETs. In this paper, we take a deep look into the metal/BP interface from the device aspects by applying different high-workfunction metals (Ni and Pd) on BP field-effect transistors with channel lengths scaling from 3  $\mu$ m down to 100 nm. Black phosphorus (BP), the bulk counterpart of phosphorene, is a stable phosphorus allotrope at room temperature. 19,20 BP has a layered structure in which individual atomic layers are stacked together by van der Waals interactions.<sup>21–23</sup> The fundamental properties of

Received for review May 9, 2014 and accepted October 14, 2014.

**Published online October 14, 2014** 10.1021/nn502553m

© 2014 American Chemical Society

<sup>\*</sup> Address correspondence to yep@purdue.edu.

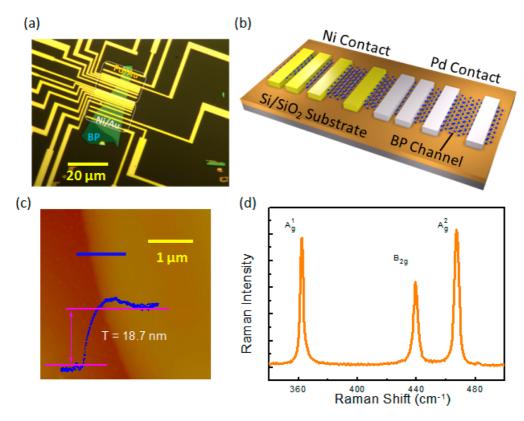

Figure 1. (a) Optical image of ultrathin BP FETs with Ni/Au and Pd/Au contacts on the same BP flake. (b) Schematic view of device configuration. A  $p^{++}$  silicon wafer capped with 90 nm of  $SiO_2$  was used as the global gate and gate dielectric, respectively. Ultrathin BP films were exfoliated from bulk BP crystals. Metal contacts with various channel lengths from 3  $\mu$ m down to 100 nm for both Ni/Au and Pd/Au were evaporated onto the same BP flake. (c) Atomic force microscopy image of this large size BP film with a measured thickness of 18.7 nm. (d) Raman spectra of the same BP film.

bulk BP had been extensively studied in the past, indicating the bulk crystal of BP is a semiconducting material with a direct band gap of 0.3 eV, <sup>19,21,23</sup> and the hole mobility in black phosphorus can reach up to 10<sup>4</sup> cm<sup>2</sup>/(V s).<sup>24</sup> The new wave of interest in BP is inspired by graphene research, an attempt to realize monolayers of BP, coined as phosphorene. Although phosphorene has been successfully exfoliated and its optical properties have been explored, 25 most of the electrical performance of the devices is demonstrated on few-layer phosphorene and ultrathin BP films. 25-29 This is because phosphorene is less stable in air, in particular in the presence of both oxygen and water.<sup>30</sup> An effective passivation technique on phosphorene is needed for practical applications. Here, we focus on ultrathin BP films since the large size of the flakes (tens of  $\mu$ m) is needed so that we can fabricate numerous FETs with two different metals on the same flake for a fair comparison, as shown in Figure 1a. Fortunately, few-layer or ultrathin 2D films are more favorable for device demonstrations because they can deliver a larger current than a monolayer in general. We determine a contact resistance of Ni and Pd on BP of 1.75  $\pm$ 0.06  $\Omega \cdot mm$  versus 3.15  $\pm$  0.15  $\Omega \cdot mm$  at a high electrostatic doping limit. Furthermore, the characteristics of BP transistors with Ni contacts can be switched from a p-type behavior to pronounced

n-type once scaled down to deep submicrometer channel lengths. The results all confirm the nature of Schottky barrier FETs for BP transistors with their smaller band gap.

### **RESULTS AND DISCUSSION**

In our experiments, a large BP flake of  $\sim$ 40  $\mu$ m  $\times$  $\sim$ 20  $\mu$ m was exfoliated from bulk BP crystal using the Scotch tape method and then transferred to a heavily doped silicon substrate with a 90 nm SiO<sub>2</sub> capping layer. Prior to device fabrication, the ultrathin BP film was soaked in acetone for 2 h to remove tape residues. Contact bars with lengths of 0.5  $\mu$ m were defined by e-beam lithography. The channel lengths are designed to be 3  $\mu$ m, 2  $\mu$ m, 1.5  $\mu$ m, 1  $\mu$ m, 500 nm, 200 nm, and 100 nm. Both 30/50 nm Ni/Au and 30/70 nm Pd/Au, deposited via e-beam evaporation, were used as contact metals on the same BP flake for a fair comparison. The optical image and schematic view of the ultrathin BP FETs are illustrated in Figure 1a and b, respectively. The thickness of BP for this study is 18.7 nm, as shown in Figure 1c, measured by atomic force microscopy (AFM). The Raman spectrum of the channel area of the BP FET is depicted in Figure 1d. The peaks at 362, 439, and 467 cm<sup>-1</sup> are due to vibrations of the crystalline lattice of the BP, and they match the Raman shifts attributed to the  $A_{g}^{1}$ ,  $B_{g}^{2}$ , and  $A_{g}^{2}$  phonon modes

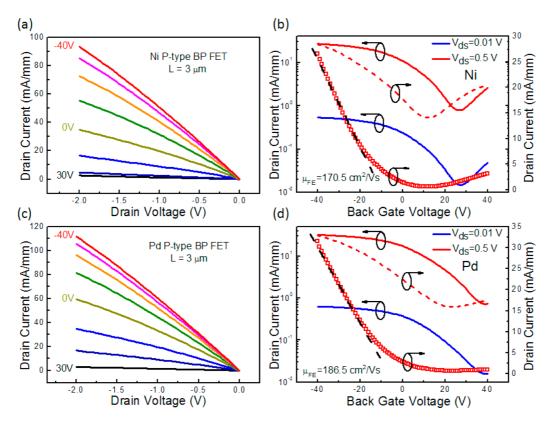

Figure 2. Device performance of p-type BP transistors for both Ni and Pd contacts. Output (a) and transfer (b) characteristics of a Ni contact BP transistor with a channel length of 3  $\mu$ m. Output (c) and transfer (d) characteristics of a Pd contact BP transistor with a channel length of 3  $\mu$ m. The arrow directions in the transfer curves stand for back gate sweep directions. Gate bias sweeps from -40 to 40 V for Ni and Pd transfer characteristics are shown in both semilogarithmic scale (red dashed lines) and linear scale (red squares).

observed in bulk black phosphorus and recent Raman studies of phosphorene. 25,27,28

I-V output characteristics of an 18.7 nm thick, 3  $\mu$ m long, BP FET with Ni contact are shown in Figure 2a with a back gate sweep from -30 to 40 V. On-state current increases as the back gate sweeps from positive voltage to negative voltage, which is a clear signature of p-type transistor behavior. The drain current varies linearly with small source/drain biases, demonstrating an ohmic-like contact resistance at the metal/BP interface with a small Schottky barrier. An onstate drain current of 93.3 mA/mm for the 3  $\mu$ m channel length in the Ni contact device is observed with  $V_{\rm bg} = -40$  V and  $V_{\rm ds} = -2$  V. The transfer curve of the Ni device measured at 0.01 and 0.5 V drain bias is shown in Figure 2b. The transistor shows a clear switching behavior with a low current on/off ratio of  $\sim 10^2$ , due to the thick flake and low band gap of BP.<sup>25–27</sup> Inspecting the transfer behavior of the p-type BP transistor, we can estimate the field-effect mobility by referring to the simple square-law theory. The extrinsic field-effect mobility,  $\mu_{FE}$ , is 170.5 cm<sup>2</sup>/(V s), as calculated from  $\mu_{FE} = g_m L/(C_{ox}V_{ds}W)$ , where  $C_{ox}$  is the capacitance of the gate oxide, W and L are the channel width and length,  $V_{ds}$  is the drain bias, and  $g_{m}$  is the peak transconductance extracted from the linear scale of transfer behaviors. The hysteresis from different

back gate sweeps is due to the fixed charges in thick SiO<sub>2</sub>, the interface traps between the BP and the SiO<sub>2</sub> substrate, and charge transfer from/to neighboring adsorbates on the BP surface. This is commonly observed on 2D devices with an exposed surface in the ambient. The I-V characteristics of the Pd contact device, as shown in Figure 2c and d, demonstrate inspiring electronic behaviors. Compared to the Ni contact device, the Pd transistor exhibits superior performance in on-state current and mobility. Examining the device with the same geometry as above, the Pd contact device has a drain current of 111.8 mA/mm and extrinsic field-effect mobility of 186.5 cm<sup>2</sup>/(V s). This larger on-state current of the Pd transistor suggests that the Pd/BP contact has a smaller contact resistance compared to the Ni/BP contact. Note that similar threshold voltages  $(V_T)$  are observed for both devices, where the  $V_T$ -induced deviation can be fairly ignored in the contact resistance comparison. However, if we take a close look at the off-state current at large positive back gate voltage from transfer curves, there is an obvious difference depending on the contact metals. For Ni BP transistors, as the back gate bias sweeps from +26 V to +40 V in Figure 2b, we clearly observe an increase in the drain current, indicating an n-type transistor behavior. As it shows both strong n-type and p-type behaviors in the drain current, it is

classified as an ambipolar transistor, which is rarely seen in previous MoS<sub>2</sub> transistor studies. However, it is barely seen in high-work-function Pd contact BP transistors, which show only a monotonic enhancement of p-type drain current with decreasing gate voltage from +40 V to -40 V. Note that the results presented here are also consistent with a previous publication.<sup>25</sup> Due to ultrathin channel thickness and improved electrostatic control, long-channel few-layer phosphorene FETs have a high current on/off ratio and negligible ambipolar behavior even with Ti or Ni contacts.<sup>25</sup> A detailed examination of the Schottky barrier effects on two contacts of BP, which will be discussed in the later parts of this paper, helps us determine the switching mechanism of BP FETs for both p-type and n-type characteristics.

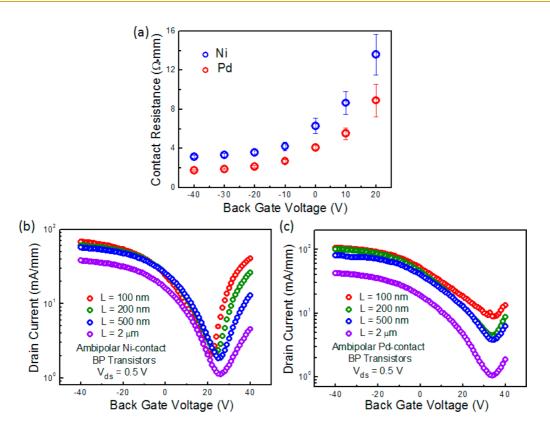

The contact resistance for both Ni and Pd contacts are extracted from the transfer length method (TLM) structure within the long-channel regime. Similar to the MoS<sub>2</sub> transistors, the contact resistance of BP transistors shows a strong gate-dependent behavior as well. The decrease of  $R_c$  at lower gate bias is related to the increase of electrostatically doped carrier density in BP under the metal contacts. The higher carrier density induced by the negative back gate voltage enhances the carrier concentration in the BP flake, which leads to a narrower Schottky barrier. Meanwhile, the narrowed Schottky barrier would thus facilitate the hole injection from the metal into the valence band of BP, leading to a lower contact resistance. 18 To exclude the large absolute errors, high negative bias regions are appropriate for a direct comparison of the contact resistance. As measured using TLM structures, the Pd contact resistance is 1.75  $\pm$  0.06  $\Omega$  · mm at  $V_{\rm bq}$  = -40 V, which is much smaller than the Ni contact resistance of  $3.15 \pm 0.15 \,\Omega \cdot \text{mm}$  at the same back gate voltage. This nearly 1.8 times reduction in contact resistance is mainly attributed to the different work function of the contact metals. The higher work-function metal Pd, with 5.4 eV, shows a significantly smaller contact resistance than the 5.0 eV metal Ni. Previous MoS<sub>2</sub> contact studies had demonstrated that the contact metals were heavily pinned near the conduction band of MoS<sub>2</sub> due to its S vacancies at the interface, where both low-work-function and high-work-function metals had similar contact resistances. 18,32 The transfer lengths ( $L_T$ ) of BP transistors are extracted by the TLM curve<sup>33</sup> and are determined to be 0.72  $\mu$ m for Pd contact and 1.18  $\mu m$  for Ni contact at the on-state for a 10-20 nm BP channel. We should note that the contact width in our experiment is designed as 0.5  $\mu$ m to maximize the number of contact bars on the same BP flake. The designed contact width is a little bit smaller than the calculated transfer length for both metals, indicating a nonfull carrier injection from the metals into the semiconductor material.<sup>34</sup> This suggests that the extracted contact resistances for both Ni

and Pd are overestimated, where the actual contact resistance should be even smaller as the contact width could be made larger than the transfer length. By examining the channel length scaling, we observed clear ambipolar characteristics for both Ni- and Pdcontacted BP FETs at shorter channel lengths. As depicted in Figure 3b and c, enhanced electron current for BP transistors exhibit a strong channel-lengthdependent behavior, where the short-channel device with a 100 nm channel length demonstrates a better n-type performance compared to the long channel length of 2  $\mu$ m. A detailed explanation for channellength-dependent ambipolar behavior will be provided later in this paper. Notably, contact metals causing an n-type performance difference between Ni and Pd is also elucidated in short-channel devices. Ambipolar behavior becomes much more pronounced if low-work-function-metal Ni is used for BP FETs. The reason for the more pronounced ambipolar behavior in Ni contact BP FETs is directly attribute to no strong Fermi-level pinning at the metal/BP interface, where the Ni metal Fermi level is closer to the conduction band, resulting in a smaller effective Schottky barrier height compared to high-work-function-metal Pd. In our experiments, a total of four sets of TLM structures, where each set is on the same BF flake, were carefully fabricated and systematically measured. The results obtained support the conclusion of minimal Fermilevel pinning at the metal/BP interface.

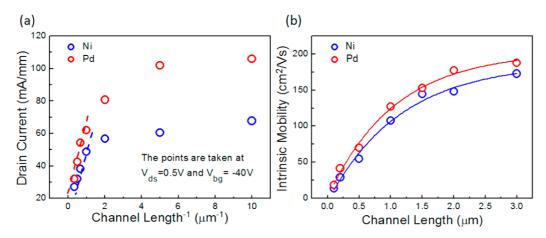

From the classical square-law theory, the drain current is inversely proportional to the channel length  $L_{ch}$ , where the drain current  $I_d$  should be presented as a linear behavior with  $1/L_{ch}$ . Shown in Figure 4a, the drain current extracted at  $V_{\rm ds} = 0.5$  V and  $V_{\rm bq} = -40$  V exhibits a linear relationship at long-channel regions. However, starting from a 500 nm  $L_{ch}$ , the drain currents begin to deviate from the inversely proportional behavior. The Pd contact current starts to saturate at 105.9 mA/mm at  $L_{ch}$  = 100 nm, and the Ni contact at 67.7 mA/mm as well. Similar to MoS<sub>2</sub> transistors, as we scale the BP FET channel length down to 500 nm, the contact resistance starts to be dominant in total resistance. The drain voltage applied on the BP FET mainly drops at the two contacts, where the contact resistance does not scale with channel length but is present in the device when the contact resistance is comparable to sheet resistance.<sup>18</sup> Next, intrinsic field-effect mobility versus channel length was studied in BP transistors. The intrinsic carrier mobility,  $\mu_{\rm FE}'$ , is estimated by  $\mu_{\rm FE}'$  =  $\mu_{\rm FE}(1-2g_{\rm m}R_{\rm c})^{-1}$ . As plotted in Figure 4b, Ni and Pd are presenting similar intrinsic field-effect mobility, indicating a good uniformity of our ultrathin BP flake, on which both Ni and Pd contacts are fabricated. Moreover, a decrease of mobility as the device channel length shrinks down to 100 nm is realized. This decrement is widely observed at any short-channel devices due to the fact that carriers are approaching their

Figure 3. (a) Contact resistance for both Ni and Pd contact metals at various gate biases. Error bars are determined from the standard errors of the linear fitting under different back gate biases. (b) I-V transfer characteristic of Ni contact BP FETs with a channel length from 2  $\mu$ m to 100 nm. (c) I-V transfer characteristic of Pd contact BP FETs with a channel length from 2  $\mu$ m to 100 nm.

Figure 4. (a) On-state drain current measured at  $-40\,\mathrm{V}$  back gate bias and 0.5 V drain bias on the set of devices fabricated with various channel lengths. The linear dependence property in the diffusive region is indicated by the dashed line. (b) Channel-length-dependent intrinsic field-effect mobility from the set of BP transistors. Ni fitting curve coincides with the Pd fitting curve showing mobility is the fundamental property of the BP film itself after extracting contact resistances.

saturation velocities at the higher electrical fields.  $^{7,18}$  The general v-E relationship represents  $v=\mu E$ , and the electrical field in the channel is inversely proportional to channel length. At the low electrical fields, the mobility is constant. However, in the short-channel case of very high electrical fields, the velocity starts to approach a value, that is, saturation velocity,  $v_s$ , due to the scattering effect and ballistic transport. Therefore, as the velocity reached the saturation value, any further increment of the electrical field by scaling the

channel length down would result in a decrement of calculated field-effect mobility. 18,34

Knowing the nature of the Schottky barrier in BP transistors is essential to understand the transistor characteristics. In the previous paragraph, we discussed how the gate bias changes the effective barrier height at the different contacts and hence controls the carrier injection at the metal/BP interface. In this part, we further discuss how the drain bias modulates the two Schottky barriers at the contacts and also the

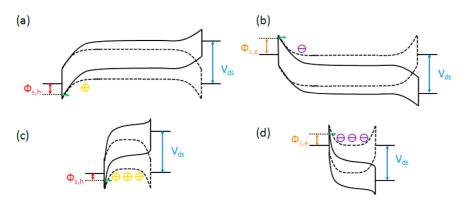

Figure 5. (a) Band diagram for a long-channel-length BP transistor with p-type behavior. The dashed line stands for  $V_{\rm ds} = 0$  V, and the solid line stands for  $V_{\rm ds} \le 0$  V. (b) Band diagram for a long-channel-length BP transistors with n-type behavior. The dashed line stands for  $V_{\rm ds} = 0$  V, and the solid line stands for  $V_{\rm ds} \ge 0$  V. (c) Band diagram for a short-channel-length BP transistor with p-type behavior. The dashed line stands for  $V_{\rm ds} = 0$  V, and the solid line stands for  $V_{\rm ds} \le 0$  V. (d) Band diagram for a short-channel-length BP transistor with n-type behavior. The dashed line stands for  $V_{\rm ds} = 0$  V, and the solid line stands for  $V_{\rm ds} \ge 0$  V.

switching mechanism of the BP transistors.<sup>34</sup> Similar to MoS<sub>2</sub> transistors, there are two asymmetrical Schottky barriers formed at the metal contacts of BP transistors, named as drain barrier and source barrier. However, compared to MoS2 transistors, where the drain bias and gate bias can control only the on and off states due to its large band gap, bias modulations in BP transistors are even more complicated and interesting. Not only can the on and off states be modulated, transistor polarization and n-type and p-type transport behaviors can also been controlled by the drain bias and gate bias. Due to BP's small band gap, the original p-type behavior of BP transistors can be easily turned into n-type transport by controlling the channel length, back gate voltages, and drain biases. This kind of transistor characteristics is not easily observed in MoS<sub>2</sub> due to its large band gap and strong contact Fermi-level pinning near the conduction band edge.<sup>35</sup>

We first define the carrier path for both p-type and n-type BP transistors from the source to drain, in which the holes and electrons would encounter the source barrier first, where the carriers would undergo a thermal-assisted tunneling process from the source metal Fermi level to the channel. On the other hand, the carriers in the channel go from the valence band or conduction band back to the drain metals, for p-type or n-type, respectively. Let us first look at the intrinsic p-type BP transistors with a long channel length, as depicted in Figure 5a. Under large negative gate biases, source and drain contacts start to form the two triangle-shaped Schottky barriers. With a further increase of the drain bias, the barrier at the source end remains constant; meanwhile, the drain barrier vanishes, facilitating carrier movement from the source to the drain.<sup>34</sup> To investigate the mechanism of characteristics switch from p-type behavior to n-type, we perform a large positive gate bias for long-channel BP transistors, shown in Figure 5b. Due to the nature of the small-band-gap structure, carriers can overcome the

Schottky barrier at the source and move along in the conduction band, showing ambipolar behavior with a moderate n-type drain current. With an adequate understanding of long-channel BP transistors, the bias-induced switching mechanism on short-channel devices remains to be elucidated. When the channel length is aggressively scaled down, the drain is close to the source, and the drain bias can start to affect the source barrier, such that the channel carrier concentration is no longer fixed. For long-channel devices, a drain bias can change the effective channel length, but the barrier at the source end is independent of the drain bias. However, for a short-channel device, the source barrier is no longer fixed. An increase of the drain bias causes the lowering of the source barrier, leading to the injection of extra carriers into the channel,<sup>36</sup> as shown in Figure 5c. It is similar to draininduced barrier lowering (DIBL) in short-channel Si MOSFETs, where the drain bias decreases the source barrier, thus enhancing the off-state current, and makes the device more difficult to turn off.36 Nevertheless, we need to carefully identify the short-channel effects related to BP transistors. In our previous publication, we proposed the drain-induced barrier narrowing (DIBN) model for MoS<sub>2</sub> transistors, where the narrowed barrier would reduce the Schottky barrier width at the source side and enhance the on-state current.<sup>34</sup> Here, we would like to describe the effect as the drain-induced characteristic switch (DICS) in BP field-effect transistors. As shown in Figure 5d, BP transistors with a short channel length under positive back gate bias and drain bias can easily experience unexpected electron movement along the conduction band, where the device demonstrates pronounced ambipolar behavior. Our experimental observations perfectly matched the proposed DICS effects, which are shown in previous results of Figure 3b and c. The scaling of the channel length down to 100 nm helps the drain bias start to have an impact on the source

ends. The lowering of the source barrier would facilitate greater electron injection into the conduction band, and the devices would exhibit stronger ambipolar behavior with enhanced n-type drain currents. The DICS effect on BP transistors will become more obvious as the channel length aggressively scales down to the sub-100 nm regime. The geometrical screening length with a planar structure is  $\lambda = ((\varepsilon_s/\varepsilon_{ox})t_st_{ox})^{1/2}$ , where  $\lambda$  is the geometrical screening length,  $\varepsilon_s = 10$  is the permittivity of BP,  $^{28,37}$   $\varepsilon_{\rm ox}$  is the permittivity of the gate oxide, and  $t_{\rm s}$ and  $t_{ox}$  are the thickness of the semiconductor channel and gate oxide. The geometrical screening length for this 18.7 nm BP flake is 65.7 nm, which is comparable to or only a little shorter than our shortest channel length device. In the extreme case where the channel length approaches the screening length, the n-type drain current becomes a strong function of the drain bias, where the n-type behavior may be dominant in BP ambipolar characteristics with a low-work-function metal, such as Y, La, or Sc. Even with Al metal contacts, our preliminary experimental result shows a

pronounced ambipolar effect at larger channel lengths. Our observations in ambipolar BP transistors open a new way to adjust transistors' polarity from p-type to n-type along with the development of doping techniques in 2D materials<sup>38</sup> and possible realization of 2D CMOS circuits based on the same channel material, BP.

#### CONCLUSION

In summary, we have studied the BP transistors' behaviors with two different high-work-function contact metals. The 0.6 eV work-function difference between Ni and Pd leads to a significantly lower contact resistance on BP using Pd. We explained the switching mechanism of BP transistors, which are controlled by two Schottky barriers at the metal contacts. Moreover, the device characteristics can be alternated from intrinsic p-type to n-type behavior by proper modulation of the channel length, gate bias, and drain bias. With the further development of doping technique and contact engineering, BP transistors show the potential for 2D CMOS logic circuits.

## **METHODS**

Multilayer BP was exfoliated from the bulk crystal black phosphorus (Smart-elements) and then transferred to a 90 nm SiO<sub>2</sub> substrate. All samples were sequentially cleaned by acetone, methanol, and 2-propanol to remove the Scotch tape residues and then stored in a nitrogen atmosphere. The thickness of the BP was measured using a Veeco Dimension 3100 atomic force microscope. The Raman optical measurement was conducted in a microscope coupled to a grating spectrometer with a CCD camera. E-beam lithography was used to define the source and drain patterns, using a Vistec VB6; 30/50 nm Ni/Au and 30/70 nm Pd/Au were deposited using e-beam evaporation under 10<sup>-6</sup> Pa pressure, with a deposition rate of 1 Å/s. No annealing was performed after the deposition of the metal contacts. Electrical measurements were carried out with a Keithley 4200 semiconductor parameter analyzer and probe station in ambient atmosphere.

Conflict of Interest: The authors declare no competing financial interest.

Acknowledgment. The authors would like to thank Zhe Luo and Xianfan Xu for optical Raman measurement, and Nathan Conrad for critical reading of the manuscript. This material is based upon work partly supported by the NSF under Grant CMMI-1120577 and SRC under Task 2396.

#### **REFERENCES AND NOTES**

- 1. Novoselov, K. S.; Geim, A. K.; Morozov, S.; Jiang, D.; Katsnelson, M.; Grigorieva, I.; Dubonos, S. V.; Firsov, A. Two-Dimensional Gas of Massless Dirac Fermions in Graphene. Nature 2005, 438, 197-200.

- 2. Zhang, Y.; Tan, Y.-W.; Stormer, H. L.; Kim, P. Experimental Observation of the Quantum Hall Effect and Berry's Phase in Graphene. Nature 2005, 438, 201-204.

- 3. Wu, Y.; Lin, Y.-M.; Bol, A. A.; Jenkins, K. A.; Xia, F.; Farmer, D. B.; Zhu, Y.; Avouris, P. High-Frequency, Scaled Graphene Transistors on Diamond-like Carbon. Nature 2011, 472, 74-78.

- 4. Jariwala, D.; Sangwan, V. K.; Lauhon, L. J.; Marks, T. J.; Hersam, M. C. Emerging Device Applications for Semiconducting Two-Dimensional Transition Metal Dichalcogenides. ACS Nano 2014, 8, 1102-1120.

- 5. Mak, K. F.; Lee, C.; Hone, J.; Shan, J.; Heinz, T. F. Atomically Thin MoS<sub>2</sub>: A New Direct-Gap Semiconductor. Phys. Rev. Lett. 2010, 105, 136805.

- 6. Radisavljevic, B.; Radenovic, A.; Brivio, J.; Giacometti, V.; Kis, A. Single-Layer MoS<sub>2</sub> Transistors. Nat. Nanotechnol. 2011, 6, 147-150.

- 7. Liu, H.; Si, M.; Najmaei, S.; Neal, A. T.; Du, Y.; Ajayan, P. M.; Lou, J.; Ye, P. D. Statistically Study of Deep Submicron Dual-Gated Field-Effect Transistors on Monolayer Chemical Vapor Deposition Molybdenum Disulfide Films. Nano Lett. 2013, 13, 2640-2646.

- Splendiani, A.; Sun, L.; Zhang, Y. B.; Li, T. S.; Kim, J.; Chim, C. Y.; Galli, G.; Wang, F. Emerging Photoluminescence in Monolayer MoS<sub>2</sub>. Nano Lett. **2010**, 10, 1271–1275.

- Yoon, Y.; Ganapathi, K.; Salahuddin, S. How Good Can Monolayer MoS<sub>2</sub> Transistors Be? Nano Lett. 2011, 11, 3768-3773.

- 10. Popov, I.; Seifert, G.; Tománek, D. Designing Electrical Contacts to MoS<sub>2</sub> Monolayers: A Computational Study. Phys. Rev. Lett. 2012, 108, 156802.

- 11. Du, Y.; Liu, H.; Neal, A. T.; Si, M.; Ye, P. D. Molecular Doping of Multilayer MoS<sub>2</sub> Field-Effect Transistors: Reduction in Sheet and Contact Resistances. IEEE Electron Device Lett. **2013**, 34, 1328-1330.

- Wang, H.; Yu, L.; Lee, Y.-H.; Shi, Y.; Hsu, A.; Chin, M. L.; Li, L.-J.; Dubey, M.: Kong, J.: Palacios, T. Integrated Circuits Based on Bilayer MoS<sub>2</sub> Transistors. Nano Lett. 2012, 12, 4674–4680.

- Liu, L.; Kumar, S.; Ouyang, Y.; Guo, J. Performance Limits of Monolayer Transition Metal Dichalcogenide Transistors. IEEE Trans. Electron Devices 2011, 58, 3042-3047.

- 14. Alam, K.; Lake, R. K. Monolayer MoS<sub>2</sub> Transistors beyond the Technology Road Map. IEEE Trans. Electron Devices **2012**, *59*, 3250-3254.

- 15. Du, Y.; Yang, L.; Zhang, J.; Liu, H.; Majumdar, K.; Kirsch, P. D.; Ye, P. D. MoS<sub>2</sub> Field-Effect Transistors with Graphene/ Metal Heterocontacts. IEEE Electron Device Lett. 2014, 35, 599-601.

- 16. Radisavljevic, B.; Kis, A. Mobility Engineering and a Metal— Insulator Transition in Monolayer MoS<sub>2</sub>. Nat. Mater. 2013, 12, 815-820.

- 17. Liu, D.; Guo, Y.; Fang, L.; Robertson, J. Sulfur Vacancies in Monolayer MoS<sub>2</sub> and Its Electrical Contacts. Appl. Phys. Lett. 2013, 103, 183113.

- 18. Liu, H.; Neal, A. T.; Ye, P. D. Channel Length Scaling of MoS<sub>2</sub> MOSFETs. ACS Nano 2012, 6, 8563-8569.

- 19. Warschauer, D. Electrical and Optical Properties of Crystalline Black Phosphorus. J. Appl. Phys. 1963, 34, 1853–1860.

- 20. Nishii, T.; Maruyama, Y.; Inabe, T.; Shirotani, I. Synthesis and Characterization of Black Phosphorus Intercalation Compounds. Synth. Met. 1987, 18, 559-564.

- 21. Narita, S.; Akahama, Y.; Tsukiyamaa, Y.; Muroa, K.; Moria, S.; Endo, S.; Taniguchi, M.; Seki, M.; Suga, S.; Mikuni, A.; et al. Electrical and Optical Properties of Black Phosphorus Single Crystals. Physica 1983, 117B-118B, 422-424.

- 22. Baba, M.; Nakamura, Y.; Takeda, Y.; Shibata, K.; Morita, A.; Koike, Y.; Fukase, T. Hall Effect and Two-Dimensional Electron Gas in Black Phosphorus. J. Phys.: Condens. Matter **1992**, 4, 1535–1544.

- 23. Maruyama, Y.; Suzuki, S.; Kobayashi, K.; Tanuma, S. Synthesis and Some Properties of Black Phosphorus Single Crystals. Physica 1981, 105B, 99-102.

- 24. Morita, A. Semiconducting Black Phosphorus. Appl. Phys. A: Mater. Sci. Process. 1986, 39, 227-242.

- 25. Liu, H.; Neal, A. T.; Zhu, Z.; Luo, Z.; Xu, X.; Tomanek, D.; Ye, P. D. Phosphorene: An Unexplored 2D Semiconductor with a High Hole Mobility. ACS Nano 2014, 8, 4033-4041.

- 26. Li, L.; Yu, Y.; Ye, G. J.; Ge, Q.; Ou, X.; Wu, H.; Feng, D.; Chen, X. H.; Zhang, Y. Black Phosphorus Field-Effect Transistors. Nat. Nanotechnol. 2014, 35.

- 27. Xia, F.; Wang, H.; Jia Y. Rediscovering Black Phosphorus: A Unique Anisotropic 2D Material for Optoelectronics and Electronics. arXiv:1402.0270.

- Gomez, A.; Vicarelli, L.; Prada, E.; Island, J. O.; Acharya, K. L. N.; Blanter, S. I.; Groenendijk, D. J.; Buscema, M.; Steele, G. A.; Alvarez, J. V.; Zandbergen, H. W.; et al. Isolation and Characterization of Few-Layer Black Phosphorus. arXiv: 1403.0499.

- 29. Koenig, S. P.; Doganov, R. A.; Schmidt, H.; Neto, A. H. C.; Ozyilmaz, B. Electrical Field Effect in Ultra-thin Black Phosphorus. Appl. Phys. Lett. 2014, 104, 103106.

- 30. Luo, W.; Zemlyanov, D.; Wu, Y. Q.; Ye, P. D. Manuscript in preparation.

- 31. Late, D. J.; Liu, B.; Matte, H. S. S. R.; Dravid, V. P.; Rao, C. N. R. Hysteresis in Single-Layer MoS<sub>2</sub> Field Effect Transistors. ACS Nano 2012, 6, 5635-5641.

- 32. Das, S.; Chen, H.-Y.; Penumatcha, A. V.; Appenzeller, J. High Performance Multilayer MoS<sub>2</sub> Transistors with Scandium Contacts. Nano Lett. 2013, 13, 100-105.

- 33. Schroder, D. K. Semiconductor Material and Device Characterization; John Wiley & Sons, 2006.

- 34. Liu, H.; Si, M.; Deng, Y.; Neal, A. T.; Du, Y.; Najmaei, S.; Ajayan, P. M.; Lou, J.; Ye, P. D. Switching Mechanism in Single-Layer Molybdenum Disulfide Transistors: An Insight into Current Flow across Schottky Barriers. ACS Nano 2014, 8, 1031-

- 35. Gong, C.; Huang, C.; Miller, J.; Cheng, L.; Hao, Y.; Cobden, D.; Kim, J.; Ruoff, R. S.; Wallace, R. M.; Cho, K.; et al. Metal Contacts on Physical Vapor Deposited Monolayer MoS<sub>2</sub>. ACS Nano 2013, 7, 11350-11357.

- 36. Sze, S. M.; Ng, K. K. Physics of Semiconductor Devices; John Wiley & Sons, 2006.

- 37. Morita, A.; Asahina, H. Band Structure and Optical Properties of Black Phosphorus. J. Phys. C: Solid State Phys. 1984,

- 38. Yang, L.; Majumdar, K.; Du, Y.; Liu, H.; Wu, H.; Hatzistergos, M.; Hung, P.; Tieckelmann, R.; Tsai, W.; Hobbs, C.; et al. High-Performance MoS<sub>2</sub> Field-Effect Transistors Enabled by Chloride Doping: Record Low Contact Resistance (0.5 k $\Omega \cdot \mu$ m) and Record High Drain Current (460  $\mu$ A/ $\mu$ m) International Symposium on VLSI Technology, 2014.